책 소개

요약

전자회로 설계 분야에서 가장 권위 있는 책으로 알려진 『Art of Electronics』의 세 번째 판이다. 1판, 2판과 마찬가지로 쉽게 이해할 수 있게 설명했으며, 3판에서는 다양하고 새로운 주제를 포함하고 기존 내용을 보강했다. 실제 회로의 동작을 보여주는 90여 개의 오실로스코프 화면과 데이터 시트에 잘 나와있지 않지만 설계할 때 필요한 수십여 개의 유용한 측정 데이터 그래프, 80개의 표(1,650개의 능동 부품) 등을 싣고 있다. 이 정보는 상용 부품들의 필수 특성(규정값과 측정값)을 나타내며, 회로 부품을 선택하는 실질적인 기준이 된다. 전자회로를 다루는 학생, 연구원, 교수, 아마추어 모두에게 없어서는 안될 참고서다.

추천의 글

“먼저 5장을 독서대에 펼치고 앉아서 읽었다. 엄청난 글이다. 과장되게 들릴 수 있으나, 내가 생각할 수 있는 유일하게 적합한 서술이다. 엄청나고, 깊고, 넓다. 특히 규격을 해석하는 설명이 좋고, 애질런트의 전압계를 분석한 내용은 정확하고 훌륭하다.”

- 故 짐 윌리엄스(Jim Williams), 리니어 테크놀로지의 아날로그 구루

“와, 5장은 내가 지난 30년 동안 경험했던 모든 회로 특성을 자세하고, 실용적이면서도 직접적으로 보여 준다. 이 책이 나만의 영업 비밀이라고 생각해 온 많은 주제를 훌륭한 그래픽과 실제 부품 번호를 통해 설명하고 있다는 점이 유일한 ‘꺼림칙함’이다. 구성이 좋다. 기기의 모든 면을 연결해 설명하려면 엄청난 노력이 들었을 것이다. 노력한 보람이 있다. 독자들이 한번에 많은 내용을 잘 이해할 수 있도록 데이터가 제시돼 있다. 좋은 책이다.”

- 존 윌리슨(John Wilison), 스탠퍼드 리서치 시스템스의 설립자

“이 분야의 종사자 중에서 작업실에 이 책 한 권을 갖추지 않은 사람이 있을까? 엔지니어, 해커, 모든 제조자여, 기뻐하라. 3판을 기다린 보람이 있다. 이 책은 전자공학을 직업으로나 취미로 탐구할 때나 도움될 수많은 맛깔나는 지식으로 차 있다. 전자공학 지식의 백과서인 이 책은 팁과 기법을 따라가면서 읽는 즐거움을 주며, 다른 책과 비교할 수 없는 참고서다! 하루를 쉬면서 한 장을 읽어 보라. 모르고 있다는 것조차 몰랐던 내용을 배우게 될 것이다. 혹은 어려운 프로젝트를 하면서 핀아웃, 도면, 기법 등 필요한 내용을 찾아보라. 전자공학이 마술이라고 생각한다면, 이 수작을 읽어 봐야 한다.”

- 리모르 ‘레이디에이다’ 프라이드(Limor ‘Ladyada’ Freid), 에이다프루트 인더스트리스

“호로위츠와 힐의 3판은 이전 판의 스타일과 내용, 기술 수준을 유지하면서 세세한 부분까지 최신 정보로 훌륭하게 증보했다. 내가 수년 동안 봐온 2판과 마찬가지로 현장의 엔지니어에게 최적이다. 호로위츠와 힐의 소탈한 스타일로 회로 설계자와 제조자에게 매우 도움되는 자세한 정보가 가득 차 있으며, 이런 내용은 다른 곳에서는 존재하지 않는다(혹은 찾기 힘들다). 우수한 증보판이며, 아날로그 회로의 기술을 아는 사람은 이 책을 확실히 좋아하게 될 것이다. H와 H에게 경의를 표한다!”

- 월트 융(Walt Jung), IC 응용 엔지니어였으며 『IC Op Amp Cookbook』의 저자

이 책에서 다루는 내용

■ 사용하기 쉬운 트랜지스터 모델

■ 전류원과 전류 복사기 같은 유용한 부분 회로들의 상세한 설명

■ 단일-전원 op-앰프 설계

■ 실제 설계 정보를 얻기 힘든 주제를 이해하기 쉽도록 설명: op-앰프 주파수 보상, 저-잡음 회로, 위상-동기 루프, 정밀 선형 설계

■ 표와 그래프를 이용한 능동 필터의 쉬운 설계

■ 잡음, 차폐, 접지

■ 저-잡음 증폭기 분석을 일관적으로 수행하는 독창적인 그래프 방식

■ 전압 기준과 레귤레이터, 일정 전류 공급원

■ 단안정 다중발진기와 특이성

■ 디지털 논리의 문제점과 대책

■ 논리 회로의 인터페이스, 새로운 NMOS와 PMOS LSI

■ A/D와 D/A 변환 기법

■ 디지털 잡음 발생

■ 미니컴퓨터, 데이터 버스 인터페이스 설명과 어셈블리 언어 소개

■ 실제 설계 예와 설명을 통한 마이크로프로세서 장: 이들을 이용해 장비를 꾸미고 원하는 것을 제작하는 방법

■ 제작 기법에 관한 장: 시제작, 인쇄 회로 기판, 장비 설계

■ 고속 스위칭 회로를 평가하는 방법

■ 과학 측정과 데이터 처리에 관한 장: 무엇을 얼마나 정확하게 측정하는지와 데이터를 처리하는 방법

■ 쉽게 설명한 대역폭 축소 방법: 신호 평균, 다중 채널 배율 조정, 록-인 증폭기, 펄스 크기 분석

■ 흥미로운 ‘나쁜 회로’ 모음과 ‘회로 아이디어’

■ 회로도를 그리는 방법, IC 종류, LC 필터 설계, 저항값, 오실로스코프, 수학 복습

■ 다이오드, 트랜지스터, FET, op-앰프, 비교기, 레귤레이터, 전압 기준, 마이크로프로세서, 기타 소자 등의 표, 많이 사용되는 것과 그 특성

■ A/D와 D/A 변환의 소자와 회로

■ 마이크로제어기에 사용되는 특수 주변기기 IC의 소개

■ 논리 계열의 선택과 논리 신호를 실제 응용으로 연결하는 방법

■ 장비 설계의 필수적인 아날로그

■ 디지털 오디오와 비디오(케이블과 위성 TV를 포함)

■ 전송선

■ SPICE 회로 시뮬레이션

■ 트랜스임피던스 증폭기

■ 공핍-모드 MOSFET

■ 보호된 MOSFET

■ 높은-쪽 구동기

■ 석영 수정 특성과 발진기

■ JFET의 철저한 검토

■ 고전압 레귤레이터

■ 광전자기

■ 전력 논리 레지스터

■ 델타-시그마 변환기

■ 정밀 다중기울기 변환

■ 메모리 기술

■ 직렬 버스

이 책의 대상 독자

전자회로 설계의 교과서와 참고서로 만들었다. 전자공학을 접해 보지 않았던 사람들에게 상당한 수준의 전자회로 설계 능력을 배우도록 했다. 회로 설계의 기본 개념을 쉽게 설명하면서도 몇 가지 주제는 심도 있게 다뤘다. 실용적인 물리학 방식과 검토된 회로 설계를 원하는 엔지니어의 정량적인 접근법을 결합하고자 했다.

하버드의 실험 전자공학 한 학기 과목에서 작성된 노트들을 기반으로 했다. 이 과목에는 다음과 같은 다양한 수강생이 있다. 과학 분야 또는 회사 취직에 필요한 기술 습득을 원하는 학부생, 연구 분야를 정한 대학원생, 급하게 ‘전자공학’이 필요하게 된 박사 과정과 후박사 과정 연구생에게 적합하다.

목차

목차

- 1장. 기초

- 1.1 도입

- 1.2 전압, 전류, 저항

- 1.2.1 전압과 전류

- 1.2.2 저항과 전류의 관계: 저항

- 1.2.3 분압기

- 1.2.4 전압원과 전류원

- 1.2.5 테브난 등가 회로

- 1.2.6 소신호 저항성분

- 1.2.7 응용 예: ‘온도가 너무 높다!’

- 1.3 신호

- 1.3.1 사인 신호

- 1.3.2 신호의 진폭과 데시벨

- 1.3.3 다른 신호

- 1.3.4 논리 수준

- 1.3.5 신호 소스

- 1.4 커패시터와 ac 회로

- 1.4.1 커패시터

- 1.4.2 RC 회로: V와 I 대비 시간

- 1.4.3 미분기

- 1.4.4 적분기

- 1.4.5 완벽하지는 않다

- 1.5 인덕터와 변압기

- 1.5.1 인덕터

- 1.5.2 변압기

- 1.6 다이오드와 다이오드 회로들

- 1.6.1 다이오드

- 1.6.2 정류

- 1.6.3 전원 필터링

- 1.6.4 전원 정류기 구성

- 1.6.5 레귤레이터

- 1.6.6 다이오드의 회로 응용

- 1.6.7 유도성 부하와 다이오드 보호

- 1.6.8 쉬어가기: 인덕터 사귀기

- 1.7 임피던스와 리액턴스

- 1.7.1 무효성 회로의 주파수 분석

- 1.7.2 인덕터의 리액턴스

- 1.7.3 복소수 전압과 전류

- 1.7.4 커패시터와 인덕터의 리액턴스

- 1.7.5 일반화된 옴의 법칙

- 1.7.6 무효성 회로의 전력

- 1.7.7 분압기의 일반화

- 1.7.8 RC 고주파통과 필터

- 1.7.9 RC 저주파통과 필터

- 1.7.10 주파수 영역의 RC 미분기와 적분기

- 1.7.11 커패시터 대비 인덕터

- 1.7.12 페이서 그래프

- 1.7.13 ‘극점’과 옥타브당 데시벨

- 1.7.14 공진 회로

- 1.7.15 LC 필터

- 1.7.16 다른 커패시터 응용들

- 1.7.17 테브난 정리의 일반화

- 1.8 종합하기–AM 라디오

- 1.9 기타 수동 부품들

- 1.9.1 전기기계적 소자: 스위치

- 1.9.2 전기기계적 소자: 계전기

- 1.9.3 커넥터

- 1.9.4 표시기

- 1.9.5 가변 소자

- 1.10 마지막 말: 헷갈리는 표식과 작은 부품들

- 1.10.1 표면 장착 기술: 즐거움과 고통

- __1장의 추가 연습

- __1장의 복습

- 2장. 바이폴라 트랜지스터

- 2.1 소개

- 2.1.1 첫 번째 트랜지스터 모델: 전류 증폭기

- 2.2 트랜지스터 기본 회로

- 2.2.1 트랜지스터 스위치

- 2.2.2 스위칭 회로 예

- 2.2.3 이미터 팔로워

- 2.2.4 전압 레귤레이터로 사용되는 이미터 팔로워

- 2.2.5 이미터 팔로워 바이어스

- 2.2.6 전류원

- 2.2.7 공통–이미터 증폭기

- 2.2.8 단위–이득 위상 분리기

- 2.2.9 트랜스컨덕턴스

- 2.3 기본 트랜지스터 회로에 적용된 에버스 - 몰 모델

- 2.3.1 개선된 트랜지스터 모델

- 트랜스컨덕턴스 증폭기

- 2.3.2 에버스-몰 모델의 결과

- 트랜지스터 설계를 위한 경험 법칙

- 2.3.3 이미터 팔로워 재고

- 2.3.4 공통–이미터 증폭기 재고

- 2.3.5 공통–이미터 증폭기에 바이어스 가하기

- 2.3.6 보충 내용: 완벽 트랜지스터

- 2.3.7 전류 반복기

- 2.3.8 차동 증폭기

- 2.4 증폭기 구성 블록

- 2.4.1 푸시 - 풀 출력단

- 2.4.2 달링턴 연결

- 2.4.3 부트스트랩핑

- 2.4.4 병렬 BJT에서 전류 공유

- 2.4.5 커패시턴스와 밀러 효과

- 2.4.6 전계-효과 트랜지스터

- 2.5 음의 되먹임

- 2.5.1 되먹임 소개

- 2.5.2 이득 공식

- 2.5.3 증폭기 회로의 되먹임 효과

- 2.5.4 두 가지 주요 세부 사항

- 2.5.5 되먹임을 갖는 트랜지스터 증폭기의 두 가지 예

- 2.6 널리 사용되는 트랜지스터 회로들

- 2.6.1 조정된 전원

- 2.6.2 온도 제어기

- 2.6.3 트랜지스터와 다이오드를 이용한 간단한 논리 회로

- __2장의 추가 연습

- __2장의 복습

- 3장. 전계-효과 트랜지스터

- 3.1 소개

- 3.1.1 FET 특성

- 3.1.2 FET 종류

- 3.1.3 보편적인 FET 특성

- 3.1.4 FET 드레인 특성

- 3.1.5 FET 특성의 제조 산포

- 3.1.6 기본 FET 회로들

- 3.2 FET 선형 회로

- 3.2.1 대표적인 JFET: 간단한 소개

- 3.2.2 JFET 전류원

- 3.2.3 FET 증폭기

- 3.2.4 차동 증폭기

- 3.2.5 발진기

- 3.2.6 소스 팔로워

- 3.2.7 가변 저항용 FET

- 3.2.8 FET 게이트 전류

- 3.3 JFET의 상세 내용

- 3.3.1 드레인 전류 대비 게이트 전압

- 3.3.2 드레인 전류 대비 드레인-소스 전압: 출력 컨덕턴스

- 3.3.3 트랜스컨덕턴스 대비 드레인 전류

- 3.3.4 트랜스컨덕턴스 대비 드레인 전압

- 3.3.5 JFET 커패시턴스

- 3.3.6 JFET 증폭기를 사용하는 이유는? (MOSFET 대비)

- 3.4 FET 스위치

- 3.4.1 FET 아날로그 스위치

- 3.4.2 FET 스위치의 한계

- 3.4.3 FET 아날로그 스위치 예

- 3.4.4 MOSFET 논리 스위치

- 3.5 전력 MOSFET

- 3.5.1 높은 임피던스, 열 안정도

- 3.5.2 전력 MOSFET 스위칭 변수

- 3.5.3 논리 수준으로 전력 스위칭

- 3.5.4 전력 스위칭 주의점

- 3.5.5 고전류 스위치용 MOSFET 대비 BJT

- 3.5.6 MOSFET 회로 예

- 3.5.7 IGBT와 기타 전력 반도체

- 3.6 선형 용도 MOSFET

- 3.6.1 고전압 압전 증폭기

- 3.6.2 공핍 모드 회로

- 3.6.3 병렬 MOSFET

- 3.6.4 열폭주

- __3장 복습

- 4장. 연산 증폭기

- 4.1 op–앰프 소개 ― ‘이상적인 부품’

- 4.1.1 되먹임과 op–앰프

- 4.1.2 연산 증폭기

- 4.1.3 황금률

- 4.2 기본 op–앰프 회로

- 4.2.1 반전 증폭기

- 4.2.2 비반전 증폭기

- 4.2.3 팔로워

- 4.2.4 차 증폭기

- 4.2.5 전류원

- 4.2.6 적분기

- 4.2.7 op–앰프 회로의 기본 주의점

- 4.3 다양한 op–앰프 회로

- 4.3.1 선형 회로들

- 4.3.2 비선형 회로들

- 4.3.3 op-앰프 응용: 삼각파 발진기

- 4.3.4 op-앰프 응용: 핀치-오프 전압 시험기

- 4.3.5 프로그램 가능한 펄스폭 발생기

- 4.3.6 능동 저주파통과 필터

- 4.4 op–앰프 동작의 상세 고찰

- 4.4.1 이상적 op-앰프 성능과의 차이

- 4.4.2 op-앰프 한계가 회로 동작에 미치는 영향

- 4.4.3 예: 민감한 밀리볼트 전압계

- 4.4.4 대역폭과 op-앰프 전류원

- 4.5 op–앰프 회로의 상세 고찰

- 4.5.1 능동 피크 감지기

- 4.5.2 표집-유지

- 4.5.3 능동 클램프

- 4.5.4 절댓값 회로

- 4.5.5 적분기의 상세 고찰

- 4.5.6 FET 누설의 회로 해법

- 4.5.7 미분기

- 4.6 단일 전원 op–앰프

- 4.6.1 단일 전원 ac 증폭기의 바이어스

- 4.6.2 용량성 부하

- 4.6.3 ‘단일 전원’ op-앰프

- 4.6.4 예제: 전압-제어 발진기

- 4.6.5 VCO 구현: 스루-홀 대비 표면 장착

- 4.6.6 영점 교차 감지기

- 4.6.7 op-앰프 표

- 4.7 다른 증폭기와 op–앰프 종류

- 4.8 대표적인 op–앰프 회로들

- 4.8.1 범용 실험실 증폭기

- 4.8.2 스턱 노드 추적기

- 4.8.3 부하-전류-감지 회로

- 4.8.4 집적 선탠 감시기

- 4.9 되먹임 증폭기의 주파수 보상

- 4.9.1 이득과 위상 이동 대비 주파수

- 4.9.2 증폭기 보상 방법

- 4.9.3 되먹임 네트워크의 주파수 응답

- __4장의 추가 연습

- __4장의 복습

- 5장. 정밀 회로

- 5.1 정밀 op–앰프 설계 기법

- 5.1.1 정밀도 대비 동적 범위

- 5.1.2 오차 예산

- 5.2 예. 밀리볼트미터, 다시 보기

- 5.2.1 난제. 10mV, 1%, 10MΩ 1.8V 단일 전원

- 5.2.2 해법. 정밀 RRIO 전류원

- 5.3 교훈. 오차 예산, 규정되지 않은 변수

- 5.4 다른 예: 영점 조정 정밀 증폭기

- 5.4.1 회로 설명

- 5.5 정밀 설계 오차 예산

- 5.5.1 오차 예산

- 5.6 부품 오차

- 5.6.1 이득-설정 저항

- 5.6.2 유지 커패시터

- 5.6.3 영점 스위치

- 5.7 증폭기의 입력 오차

- 5.7.1 입력 임피던스

- 5.7.2 입력 바이어스 전류

- 5.7.3 전압 오프셋

- 5.7.4 공통-모드 억제

- 5.7.5 전원 제거

- 5.7.6 영점 조정 증폭기: 입력 오차

- 5.8 증폭기의 출력 오차

- 5.8.1 슬루율. 일반적인 고찰

- 5.8.2 대역폭과 정정 시간

- 5.8.3 교차 왜곡과 출력 임피던스

- 5.8.4 단위-이득 전력 버퍼

- 5.8.5 이득 오차

- 5.8.6 이득 비선형성

- 5.8.7 위상 오차와 ‘능동 보상’

- 5.9 RRIO op–앰프. 장단점

- 5.9.1 입력 문제

- 5.9.2 출력 문제

- 5.10 정밀 op–앰프의 선택

- 5.10.1 ‘7개의 정밀 op-앰프’

- 5.10.2 패키지당 개수

- 5.10.3 전원 전압, 신호 범위

- 5.10.4 단일-전원 동작

- 5.10.5 오프셋 전압

- 5.10.6 전압 잡음

- 5.10.7 바이어스 전류

- 5.10.8 전류 잡음

- 5.10.9 CMRR과 PSRR

- 5.10.10 GBW, fT, 슬루율, ‘m’, 정정 시간

- 5.10.11 왜곡

- 5.10.12 ‘셋 중 둘은 나쁘지 않음’: 완벽한 op -앰프의 설계

- 5.11 자동–영점(초퍼–안정화) 증폭기

- 5.11.1 자동-영점 op-앰프 특성

- 5.11.2 자동-영점 op-앰프의 사용처

- 5.11.3 자동-영점 op-앰프의 선택

- 5.11.4 자동-영점 기타 사항

- 5.12 고수들의 설계: 에질런트의 정밀 DMM

- 5.12.1 불가능하다!

- 5.12.2 틀렸다-가능하다!

- 5.12.3 블록 다이어그램. 간단한 설계

- 5.12.4 34401A 6.5-자릿수 전단부

- 5.12.5 34420A 7.5-자릿수 전단부

- 5.13 차, 차동, 장비용 증폭기: 소개

- 5.14 차 증폭기

- 5.14.1 기본 회로 동작

- 5.14.2 응용예

- 5.14.3 성능 변수

- 5.14.4 회로 변형

- 5.15 장비용 증폭기

- 5.15.1 첫 번째(그러나 단순한) 시도

- 5.15.2 클래식 삼중-op-앰프 장비용 증폭기

- 5.15.3 입력단 고려 사항

- 5.15.4 ‘자작’ 장비용 증폭기

- 5.15.5 단단한 입력 보호 재고

- 5.16 장비용 증폭기 기타 사항

- 5.16.1 입력 전류와 잡음

- 5.16.2 공통-모드 억제

- 5.16.3 소스 임피던스와 CMRR

- 5.16.4 EMI와 입력 보호

- 5.16.5 오프셋과 CMRR 보정

- 5.16.6 부하에서 감지

- 5.16.7 입력 바이어스 경로

- 5.16.8 출력 전압 범위

- 5.16.9 응용예: 전류원

- 5.16.10 다른 구성

- 5.16.11 초퍼와 자동-영점 장비용 증폭기

- 5.16.12 이득을 프로그램하는 장비용 증폭기

- 5.16.13 차동 출력의 발생

- 5.17 완전 차동 증폭기

- 5.17.1 차동 증폭기. 기본 개념

- 5.17.2 차동 증폭기 응용예. 광대역 아날로그 링크

- 5.17.3 차동-입력 ADC

- 5.17.4 임피던스 정합

- 5.17.5 차동 증폭기 선택 기준

- __5장의 복습

- 6장. 필터

- 6.1 소개

- 6.2 수동 필터

- 6.2.1 RC 필터의 주파수 응답

- 6.2.2 LC 필터의 이상적인 성능

- 6.2.3 몇 가지 단순한 예

- 6.2.4 능동 필터 도입: 개요

- 6.2.5 필터 성능의 주요 기준

- 6.2.6 필터 종류

- 6.2.7 필터 구현

- 6.3 능동–필터 회로

- 6.3.1 VCVS 회로

- 6.3.2 간단한 표를 이용한 VCVS 필터 설계

- 6.3.3 상태변수 필터

- 6.3.4 쌍-T 노치 필터

- 6.3.5 전역통과 필터

- 6.3.6 스위치드-커패시터 필터

- 6.3.7 디지털 신호 처리

- 6.3.8 필터 기타 사항

- __6장의 추가 연습

- __6장의 복습

- 7장. 발진기와 타이머

- 7.1 발진기

- 7.1.1 발진기 소개

- 7.1.2 완화 발진기

- 7.1.3 클래식 발진기-타이머 칩. 555

- 7.1.4 기타 완화-발진기 IC

- 7.1.5 사인파 발진기

- 7.1.6 수정 발진기

- 7.1.7 높은 안정성. TCXO, OCXO, 그리고 그 이상의 기법

- 7.1.8 주파수 합성: DDS와 PLL

- 7.1.9 직교 발진기

- 7.1.10 발진기 ‘지터’

- 7.2 타이머

- 7.2.1 스텝으로 트리거되는 펄스

- 7.2.2 단안정 다중진동기

- 7.2.3 단안정기 응용. 펄스 폭과 동작 주기

- 7.2.4 디지털 계수기를 사용한 타이밍

- __7장의 복습

- 8장. 저잡음 기법

- 8.1 ‘잡음’

- 8.1.1 존슨(나이키스트) 잡음

- 8.1.2 샷 잡음

- 8.1.3 1/f 잡음(플리커 잡음)

- 8.1.4 버스트(Burst) 잡음

- 8.1.5 대역-제한 잡음

- 8.1.6 간섭

- 8.2 신호–잡음비와 잡음 지수

- 8.2.1 잡음 전력 밀도와 대역폭

- 8.2.2 신호 대 잡음 비

- 8.2.3 잡음 지수

- 8.2.4 잡음 온도

- 8.3 바이폴라 트랜지스터 증폭기 잡음

- 8.3.1 전압 잡음, e_n

- 8.3.2 전류 잡음 i_n

- 8.3.3 BJT 전압 잡음 재고

- 8.3.4 간단한 설계 예. 마이크 용도의 확성기

- 8.3.5 전류원과 이미터 팔로워의 샷 잡음

- 8.4 잡음 지수 규격에서 e_n

- 8.4.1 스텝 1: NF 대비 I_C

- 8.4.2 스텝 2: NF 대비 R_S

- 8.4.3 스텝 3: e_n 구하기

- 8.4.4 스텝 4: e_n 스펙트럼

- 8.4.5 i_n의 스펙트럼

- 8.4.6 동작 전류를 바꿀 수 없는 경우

- 8.5 바이폴라 트랜지스터의 저잡음 설계

- 8.5.1 잡음 지수 예

- 8.5.2 en과 in으로 증폭기 잡음을 표시하기

- 8.5.3 잡음 저항값

- 8.5.4 비교 잡음을 표시하기

- 8.5.5 BJT의 저잡음 설계: 두 가지 예

- 8.5.6 최소 잡음: BJT, FET, 변압기

- 8.5.7 설계 예. 40¢ ‘번개 감지기’ 전단 증폭기

- 8.5.8 저잡음 바이폴라 트랜지스터의 선택

- 8.5.9 극저잡음 설계 문제. 변압기가 없는 리본 마이크 전단 증폭기

- 8.6 JFET를 이용한 저잡음 설계

- 8.6.1 JFET의 전압 잡음

- 8.6.2 JFET의 전류 잡음

- 8.6.3 설계 예: 저잡음 광대역 JFET ‘혼성’ 증폭기

- 8.6.4 고수의 설계. SR560 저잡음 전단 증폭기

- 8.6.5 저잡음 JFET의 선택

- 8.7 바이폴라–FET 비교

- 8.7.1 MOSFET은 어떤가?

- 8.8 차동 되먹임 증폭기의 잡음

- 8.9 연산 증폭기 회로의 잡음

- 8.9.1 표 8.3. 저잡음 op-amp의 선택

- 8.9.2 전원 제거비

- 8.9.3 정리: 저잡음 op-앰프의 선택

- 8.9.4 저잡음 장비용 증폭기와 비디오 증폭기

- 8.9.5 저잡음 혼성 op-앰프

- 8.10 신호 변압기

- 8.10.1 변압기 되먹임을 갖는 저잡음 광대역 증폭기

- 8.11 트랜스임피던스 증폭기의 잡음

- 8.11.1 안정성 문제의 요약

- 8.11.2 증폭기 입력 잡음

- 8.11.3 e_nC 잡음 문제

- 8.11.4 트랜스저항 증폭기의 잡음

- 8.11.5 예제: 광대역 JFET 광다이오드 증폭기

- 8.11.6 트랜스임피던스 증폭기의 잡음 대비 이득

- 8.11.7 트랜스임피던스 증폭기의 출력 대역폭 제한

- 8.11.8 복합 트랜스임피던스 증폭기

- 8.11.9 입력 커패시턴스 줄이기: 트랜스임피던스 증폭기에 부트스트랩 걸기

- 8.11.10 입력 커패시턴스의 격리: 트랜스임피던스 증폭기에 캐스코드 달기

- 8.11.11 용량성 되먹임을 갖는 트랜스임피던스 증폭기

- 8.11.12 주사 터널링 마이크로스코프 전단 증폭기

- 8.11.13 보상과 조절을 위한 측정 기구

- 8.11.14 마지막 언급

- 8.12 잡음 측정과 잡음원

- 8.12.1 잡음원이 없는 측정

- 8.12.2 예제: 트랜지스터 잡음 테스트 회로

- 8.12.3 잡음원을 포함하는 측정

- 8.12.4 잡음과 신호원

- 8.13 대역폭 제한과 rms 전압 측정

- 8.13.1 대역폭 제한

- 8.13.2 적분된 잡음의 계산

- 8.13.3 비대칭 필터를 이용한 op-앰프의 ‘저주파 잡음’

- 8.13.4 1/f 모서리 주파수 찾기

- 8.13.5 잡음 전압의 측정

- 8.13.6 잡음 전류의 측정

- 8.13.7 다른 방법: fA/√‾ Hz 장비의 자작

- 8.13.8 잡음 기타 사항

- 8.14 대역폭 제한을 통한 신호–잡음의 개선

- 8.14.1 록-인 검출

- 8.15 전원 잡음

- 8.15.1 커패시턴스 증배기

- 8.16 간섭, 차폐, 접지

- 8.16.1 간섭 신호

- 8.16.2 신호 접지

- 8.16.3 장비 사이의 접지

- __8장의 추가 연습문제

- __8장의 복습

- 9장. 레귤레이션과 전력 변환

- 9.1 소개: 제너에서 직렬–통과 선형 레귤레이터까지

- 9.1.1 되먹임의 추가

- 9.2 클래식 723을 이용한 기본 선형 레귤레이터 회로

- 9.2.1 723 레귤레이터

- 9.2.2 723의 변론

- 9.3 완전히 집적된 선형 레귤레이터

- 9.3.1 선형 레귤레이터 IC의 분류

- 9.3.2 3-단자 고정 레귤레이터

- 9.3.3 3-단자 가변 레귤레이터

- 9.3.4 317 형 레귤레이터: 응용 힌트

- 9.3.5 317형 레귤레이터: 회로 예

- 9.3.6 더 낮은 강하의 레귤레이터

- 9.3.7 진정한 저강하 레귤레이터

- 9.3.8 전류-기준 3-단자 레귤레이터

- 9.3.9 강하 전압의 비교

- 9.3.10 이중-전압 레귤레이터 회로 예

- 9.3.11 선형 레귤레이터 선택

- 9.3.12 선형 레귤레이터 특이점

- 9.3.13 잡음과 리플 필터링

- 9.3.14 전류원

- 9.4 열과 전력 설계

- 9.4.1 전력 트랜지스터와 방열기

- 9.4.2 안전 동작 영역

- 9.5 ac 선로에서 비조정 선로까지

- 9.5.1 ac-선로 부품들

- 9.5.2 변압기

- 9.5.3 dc 부품

- 9.5.4 비조정 분리 전원-실험!

- 9.5.5 선형 대비 스위처: 리플과 잡음

- 9.6 스위칭 레귤레이터와 dc–dc 변환기

- 9.6.1 선형 대비 스위칭

- 9.6.2 스위칭 변환기 구조

- 9.6.3 인덕터가 없는 스위칭 변환기

- 9.6.4 인덕터를 가진 변환기: 기본적인 비격리 구조

- 9.6.5 스텝-다운(벅) 변환기

- 9.6.6 스텝-업(부스트) 변환기

- 9.6.7 반전 변환기

- 9.6.8 비격리 변환기에 대한 추가 설명

- 9.6.9 전압 모드와 전류 모드

- 9.6.10 변압기를 갖는 변환기: 기본 설계

- 9.6.11 플라이백 변환기

- 9.6.12 순방향 변환기

- 9.6.13 브리지 변환기

- 9.7 AC–선로–구동(‘직접–선로’) 스위칭 변환기

- 9.7.1 ac-dc 입력단

- 9.7.2 dc-dc 변환기

- 9.8 스위처의 실제 예

- 9.8.1 스위처: 개요

- 9.8.2 스위처: 기본 동작

- 9.8.3 스위처: 상세 고찰

- 9.8.4 ‘기준 설계’

- 9.8.5 정리: 선로-구동 스위칭 전원에 관한 일반적인 언급

- 9.8.6 스위처를 사용하는 경우

- 9.9 인버터와 스위칭 증폭기

- 9.10 전압 기준

- 9.10.1 제너 다이오드

- 9.10.2 밴드갭(VBE) 기준

- 9.10.3 JFET 핀치-오프(VP) 기준

- 9.10.4 부유-게이트 기준

- 9.10.5 3-단자 정밀 기준

- 9.10.6 전압 기준의 잡음

- 9.10.7 전압 기준: 기타 사항들

- 9.11 상용 전원 모듈

- 9.12 에너지 저장: 배터리와 커패시터

- 9.12.1 배터리 특성

- 9.12.2 배터리 선택

- 9.12.3 커패시터에 에너지 저장

- 9.13 전력 조정의 추가 사항들

- 9.13.1 과전압 방지기

- 9.13.2 입력-전압 범위의 확장

- 9.13.3 폴드백 전류 제한

- 9.13.4 외부 통과 트랜지스터

- 9.13.5 고전압 레귤레이터

- __9장의 복습

- 10장. 디지털 논리

- 10.1 기본 논리 개념

- 10.1.1 디지털 대비 아날로그

- 10.1.2 논리 상태

- 10.1.3 숫자 코드

- 10.1.4 게이트와 진실표

- 10.1.5 개별 회로 게이트

- 10.1.6 게이트-논리 예

- 10.1.7 주장-값 논리 표시

- 10.2 디지털 집적 회로: CMOS와 바이폴라

- 10.2.1 일반 게이트 카탈로그

- 10.2.2 IC 게이트 회로

- 10.2.3 CMOS와 바이폴라(‘TTL’) 특성

- 10.2.4 3-상태와 개방-컬렉터 소자

- 10.3 조합 논리

- 10.3.1 논리 등가

- 10.3.2 최소화와 카르노 표

- 10.3.3 IC로 나와 있는 조합 함수

- 10.4 순차 논리

- 10.4.1 메모리를 갖는 소자: 플립-플롭

- 10.4.2 클럭이 있는 플립-플롭

- 10.4.3 메모리와 게이트의 결합: 순차 논리

- 10.4.4 동기화기

- 10.4.5 단안정 다중진동기

- 10.4.6 플립-플롭과 계수기를 이용한 단일-펄스 발생

- 10.5 집적 회로로 나와 있는 순차 함수

- 10.5.1 래치와 레지스터

- 10.5.2 계수기

- 10.5.3 시프트 레지스터

- 10.5.4 프로그램형 논리 소자

- 10.5.5 기타 순차 함수

- 10.6 대표적 디지털 회로

- 10.6.1 모듈로-n 계수기: 타이밍 예

- 10.6.2 다중화 LED 디지털 디스플레이

- 10.6.3 n-펄스 발생기

- 10.7 미소전력 디지털 설계

- 10.7.1 CMOS 저전력을 유지하기

- 10.8 논리 회로 증상 분석

- 10.8.1 dc 문제

- 10.8.2 스위칭 문제

- 10.8.3 TTL과 CMOS의 근본적인 문제

- __10장의 추가 연습

- __10장의 복습

- 11장. 프로그램형 논리 장치

- 11.1 내력

- 11.2 하드웨어

- 11.2.1 기본적인 PAL

- 11.2.2 PLA

- 11.2.3 FPGA

- 11.2.4 구성 메모리

- 11.2.5 기타 프로그램형 논리 장치

- 11.2.6 소프트웨어

- 11.3 예: 의사난수 바이트 발생기

- 11.3.1 의사난수 바이트를 만드는 방법

- 11.3.2 표준 논리로 구현

- 11.3.3 프로그램형 논리로 구현

- 11.3.4 프로그램형 논리-HDL 작성

- 11.3.5 마이크로제어기로 구현

- 11.4 도움말

- 11.4.1 기술 종류

- 11.4.2 사용자 집단

- __11장의 복습

- 12장. 논리 인터페이스

- 12.1 CMOS와 TTL 논리 인터페이스

- 12.1.1 논리 계열의 연대-간단한 역사

- 12.1.2 입력과 출력 특성

- 12.1.3 논리 계열 사이의 인터페이스

- 12.1.4 디지털 논리 입력의 구동

- 12.1.5 입력 보호

- 12.1.6 논리 입력에 관한 추가 설명

- 12.1.7 비교기 또는 op-앰프로 디지털 논리를 구동하기

- 12.2 보충 내용: 디지털 신호의 측정

- 12.3 비교기

- 12.3.1 출력

- 12.3.2 입력

- 12.3.3 다른 변수들

- 12.3.4 기타 주의점

- 12.4 논리값으로 외부 디지털 부하를 구동하기

- 12.4.1 양 부하: 직접 구동

- 12.4.2 양의 부하: 트랜지스터 구동

- 12.4.3 음 또는 ac 부하

- 12.4.4 전원 스위치의 보호

- 12.4.5 nMOS LSI 인터페이스

- 12.5 광전자: 이미터

- 12.5.1 표시기와 LED

- 12.5.2 레이저 다이오드

- 12.5.3 디스플레이

- 12.6 광전자: 검출기

- 12.6.1 광다이오드와 광트랜지스터

- 12.6.2 광증배기

- 12.7 광결합기와 계전기

- 12.7.1 I: 광트랜지스터 출력 광결합기

- 12.7.2 II: 논리-출력 광결합기

- 12.7.3 III: 게이트 구동기 광결합기

- 12.7.4 IV: 아날로그 광결합기

- 12.7.5 V: 고체 계전기(트랜지스터 출력)

- 12.7.6 VI: 고체 계전기(트라이액/SCR 출력)

- 12.7.7 VII: ac-입력 광결합기

- 12.7.8 인터럽터

- 12.8 광전자기: 광섬유 디지털 링크

- 12.8.1 토스링크

- 12.8.2 버사타일 링크

- 12.8.3 ST/SC 유리-섬유 모듈

- 12.8.4 완전히 집적된 고속 섬유-송수신기 모듈

- 12.9 디지털 신호와 긴 연결선

- 12.9.1 보드 위의 연결

- 12.9.2 카드 사이의 연결

- 12.10 케이블 구동하기

- 12.10.1 동축 케이블

- 12.10.2 바른 방법-I: 원단 종단

- 12.10.3 차동쌍 케이블

- 12.10.4 RS-232

- 12.10.5 정리

- __12장의 복습

- 13장. 디지털과 아날로그의 만남

- 13.1 사전 지식

- 13.1.1 기본 성능 변수

- 13.1.2 코드

- 13.1.3 변환기 에러

- 13.1.4 개별 소자 대비 집적된 ADC

- 13.2 디지털–아날로그 변환기

- 13.2.1 저항열 DAC

- 13.2.2 R-2R 사다리 DAC

- 13.2.3 전류-스티어링 DAC

- 13.2.4 승산 DAC

- 13.2.5 전압 출력의 발생

- 13.2.6 여섯 가지 DAC

- 13.2.7 델타-시그마 DAC

- 13.2.8 디지털-아날로그 변환기 PWM

- 13.2.9 주파수-전압 변환

- 13.2.10 속도 증배기

- 13.2.11 DAC 선택

- 13.3 DAC 응용 예

- 13.3.1 범용 실험실 신호원

- 13.3.2 8채널 신호원

- 13.3.3 나노앰프, 넓은-허용 전압 범위, 양극성 전류원

- 13.3.4 정밀 코일 구동기

- 13.4 변환기 선형성–상세 고찰

- 13.5 아날로그–디지털 변환기

- 13.5.1 계수화: 에일리어싱, 표집 속도, 표집 깊이

- 13.5.2 ADC 기법

- 13.6 ADC I: 병렬(‘플래시’) 부호기

- 13.6.1 변경된 플래시 부호기

- 13.6.2 플래시, 폴딩, RF ADC의 구동

- 13.6.3 부족 표집 플래시-변환기 예

- 13.7 ADC II: 연속 근사법

- 13.7.1 간단한 SAR 예

- 13.7.2 연속 근사의 변형

- 13.7.3 A/D 변환 예

- 13.8 ADC III: 적분

- 13.8.1 전압-주파수 변환

- 13.8.2 단일-기울기 적분

- 13.8.3 적분 변환기

- 13.8.4 이중-기울기 적분

- 13.8.5 변환 응용의 아날로그 스위치들

- 13.8.6 대가의 설계들: 애질런트의 최상급 ‘다중 기울기’ 변환기들

- 13.9 ADC IV: 델타–시그마

- 13.9.1 선탠 감시를 위한 간단한 델타-시그마

- 13.9.2 델타-시그마 변환기의 해설

- 13.9.3 DΣ ADC와 DAC

- 13.9.4 DΣ 과정

- 13.9.5 부가 설명: ‘잡음 정형’

- 13.9.6 기본 사실

- 13.9.7 모의 실험

- 13.9.8 DAC는?

- 13.9.9 DΣ 과표집 변환기의 장점과 단점

- 13.9.10 무부하 톤

- 13.9.11 델타-시그마 응용 예

- 13.10 ADC: 선택과 타협

- 13.10.1 델타-시그마와 경쟁 기술

- 13.10.2 표집 대비 평균 ADC: 잡음

- 13.10.3 미소 전력 A/D 변환기

- 13.11 특수 A/D와 D/A 변환기

- 13.11.1 ADE7753 다기능 ac 전력 계측 IC

- 13.11.2 AD7873 터치스크린 수치화기

- 13.11.3 순서기를 가진 AD7927 ADC

- 13.11.4 AD7730 정밀 브리지-측정 부시스템

- 13.12 A/D 변환 시스템 예

- 13.12.1 다중화 16채널 데이터-획득 시스템

- 13.12.2 병렬 다중채널 연속-근사 데이터-획득 시스템

- 13.12.3 병렬 다중채널 델타-시그마 데이터-획득 시스템

- 13.13 위상–동기 루프

- 13.13.1 위상-동기 루프의 소개

- 13.13.2 PLL 요소들

- 13.13.3 PLL 설계

- 13.13.4 설계 예: 주파수 증배기

- 13.13.5 PLL 획득과 동기

- 13.13.6 몇 가지 PLL 응용

- 13.13.7 정리: PLL의 잡음과 지터 억제

- 13.14 의사 임의 비트 순열과 잡음 발생

- 13.14.1 디지털-잡음 발생

- 13.4.2 되먹임 시프트 레지스터 순열

- 13.4.3 최대-길이 순열을 이용한 아날로그 잡음 발생

- 13.14.4 시프트-레지스터 순열의 전력 스펙트럼

- 13.14.5 저주파통과 필터링

- 13.14.6 정리

- 13.14.7 ‘진정한’ 임의 잡음 발생기

- 13.14.8 ‘혼성 디지털 필터’

- __13장의 추가 연습 문제들

- __13장의 복습

- 14장. 컴퓨터, 제어기, 데이터 링크

- 14.1 컴퓨터 구조: CPU와 데이터 버스

- 14.1.1 CPU

- 14.1.2 메모리

- 14.1.3 대용량 메모리

- 14.1.4 그래픽, 네트워크, 병렬과 직렬 포트

- 14.1.5 실시간 I/O

- 14.1.6 데이터 버스

- 14.2 컴퓨터 명령어 집합

- 14.2.1 어셈블리어와 기계어

- 14.2.2 간단한 ‘x86’ 명령어 집합

- 14.2.3 프로그래밍 예

- 14.3 버스 신호와 인터페이스

- 14.3.1 기본적인 버스 신호들: 데이터, 주소, 스트로브

- 14.3.2 프로그램된 I/O: 데이터 출력

- 14.3.3 XY 벡터 디스플레이의 프로그래밍

- 14.3.4 프로그램된 I/O: 데이터 입력

- 14.3.5 프로그램된 I/O: 상태 레지스터

- 14.3.6 프로그램된 I/O: 명령어 레지스터

- 14.3.7 인터럽트

- 14.3.8 인터럽트 처리

- 14.3.9 일반적인 인터럽트

- 14.3.10 직접 메모리 접근

- 14.3.11 PC104/ISA 8비트 버스 신호의 요약

- 14.3.12 내장 단일-보드 컴퓨터로 사용되는 PC104

- 14.4 메모리 종류

- 14.4.1 휘발성과 비휘발성 메모리

- 14.4.2 정적 대비 동적 RAM

- 14.4.3 정적 RAM

- 14.4.4 동적 RAM

- 14.4.5 비휘발성 메모리

- 14.4.6 메모리 요약

- 14.5 기타 버스와 데이터 링크: 개요

- 14.6 병렬 버스와 데이터 링크

- 14.6.1 병렬 칩 ‘버스’ 인터페이스 - 예

- 14.6.2 병렬 칩 데이터 링크 - 두 가지 고속 예

- 14.6.3 기타 병렬 컴퓨터 버스들

- 14.6.4 병렬 주변장치 버스와 데이터 링크

- 14.7 직렬 버스와 데이터 링크

- 14.7.1 SPI

- 14.7.2 I2C 2선 인터페이스(‘TWI’)

- 14.7.3 달라스-맥심 ‘1선’ 직렬 인터페이스

- 14.7.4 JTAG

- 14.7.5 사라진 클럭: 클럭 복구

- 14.7.6 SATA, eSATA, SAS

- 14.7.7 PCI 익스프레스

- 14.7.8 비동기식 직렬(RS-232, RS-485)

- 14.7.9 맨체스터 코딩

- 14.7.10 2상 코딩

- 14.7.11 RLL 2진: 비트 채우기

- 14.7.12 RLL 코딩: 8b/10b와 기타

- 14.7.13 USB

- 14.7.14 파이어와이어

- 14.7.15 관제구 통신망(CAN)

- 14.7.16 이더넷

- 14.8 숫자 형식

- 14.8.1 정수

- 14.8.2 부동-소수점 숫자

- __14장의 복습

- 15장. 마이크로제어기

- 15.1 소개

- 15.2 설계 예 1: 선탠 모니터(V)

- 15.2.1 마이크로제어기 구현

- 15.2.2 마이크로제어기 코드(‘펌웨어’)

- 15.3 일반 마이크로제어기 계열의 개요

- 15.3.1 칩상 주변장치들

- 15.4 설계 예 2: ac 전원 제어

- 15.4.1 마이크로제어기 구현

- 15.4.2 마이크로제어기 코드

- 15.5 설계 예 3: 주파수 합성기

- 15.5.1 마이크로제어기 코드

- 15.6 설계 예 4: 온도 제어기

- 15.6.1 하드웨어

- 15.6.2 제어 루프

- 15.6.3 마이크로제어기 코드

- 15.7 설계 예 5: 안정화된 기계식 발판

- 15.8 마이크로제어기를 위한 주변장치 IC

- 15.8.1 직접 연결된 주변장치

- 15.8.2 SPI 연결을 갖는 주변장치

- 15.8.3 I2C 연결을 갖는 주변장치

- 15.8.4 중요한 하드웨어 제한 사항

- 15.9 개발 환경

- 15.9.1 소프트웨어

- 15.9.2 실시간 프로그래밍 제한

- 15.9.3 하드웨어

- 15.9.4 아두이노 프로젝트

- 15.10 마무리

- 15.10.1 툴의 가격은 얼마인가?

- 15.10.2 마이크로제어기는 언제 사용하는가?

- 15.10.3 마이크로제어기를 선택하는 방법

- 15.10.4 끝말

- __15장의 복습

- 부록 A. 수학 검토

- A.1 삼각법, 지수, 로그

- A.2 복소수

- A.3 미분(대수)

- A.3.1 일반 함수들의 미분

- A.3.2 복합 미분의 법칙들

- A.3.3 미분의 예

- 부록 B. 회로도를 그리는 방법

- B.1 일반 원칙

- B.2 규칙

- B.3 힌트

- B.4 쉬운 예

- 부록 C. 저항 종류

- C.1 역사

- C.2 구할 수 있는 저항값

- C.3 저항 표식

- C.4 저항 종류

- C.5 헷갈리는 표식

- 부록 D. 테브난 정리

- D.1 증명

- D.1.1 두 예제 - 전압 나눔기

- D.2 노턴 정리

- D.3 다른 예

- D.4 밀만의 정리

- 부록 E. LC 버터워스 필터

- E.1 저주파통과 필터

- E.2 고주파통과 필터

- E.3 필터 예

- 부록 F. 부하선

- F.1 예

- F.2 3단자 소자

- F.3 비선형 소자

- 부록 G. 커브 트레이서

- 부록 H. 전송선과 임피던스 정합

- H.1 전송선의 특성

- H.1.1 특성 임피던스

- H.1.2 종단: 펄스

- H.1.3 종단: 사인 신호

- H.1.4 전송선의 손실

- H.2 임피던스 정합

- H.2.1 저항성(유손실) 광대역 정합 네트워크

- H.2.2 저항성 감쇠기

- H.2.3 변압기(무손실) 광대역 정합 네트워크

- H.2.4 무효성(무손실) 협대역 정합 네트워크

- H.3 집중 요소 지연선과 펄스 형성 네트워크

- H.4 후기: 특성 임피던스의 사다리 유도

- H.4.1 첫 번째 방법: 종단된 선로

- H.4.2 두 번째 방법: 반무한선

- H.4.3 후기: 집중 요소 지연선

- 부록 I. TV: 간단한 지침서

- I.1 TV: 비디오와 오디오

- I.1.1 오디오

- I.1.2 비디오

- I.2 오디오+비디오를 합해 보내기: 변조

- I.3 아날로그 형식 방송 또는 케이블 TV를 녹화하기

- I.4 디지털 TV: 무엇인가?

- I.5 디지털 TV: 방송 그리고 케이블 전송

- I.6 직접 위성 TV

- I.7 인터넷을 통한 디지털 비디오 스트리밍.

- I.8 디지털 케이블: 우대 서비스와 조건부 시청

- I.8.1 디지털 케이블: 비디오-온-디맨드

- I.8.2 디지털 케이블: 교환 방송

- I.9 디지털 TV의 녹화

- I.10 디스플레이 기술

- I.11 비디오 연결: 아날로그(컴포짓과 컴포넌트)과 디지털(HDMI/DVI, 디스플레이포트)

- 부록 J. SPICE 입문: 무료 ICAP/4 데모 버전으로 시작하기

- J.1 ICAP SPICE의 설치

- J.2 회로도 입력

- J.3 시뮬레이션 돌리기

- J.3.1 회로도 입력

- J.3.2 시뮬레이션: 주파수 스윕

- J.3.3 시뮬레이션: 입력과 출력 파형

- J.4 추가 설명

- J.5 상세 예: 증폭기 왜곡을 검토하기

- J.6 부품 데이터베이스를 확장하기

- 부록 K. 전자 부품을 사려면 어디로 가야 하는가?’

- __I. 우편 주문과 온라인

- __II. 인덱스와 검색

- __III. 근처 판매점

- __IV. 기타

- 부록 L. 작업벤치 기기와 도구

- 부록 M. 카탈로그, 잡지, 데이터북

- 부록 N. 추가 읽을거리와 참고 문헌

- __일반 서적

- __핸드북

- __BJT와 FET

- __SPICE

- __증폭기, 트랜스듀서, 잡음

- __Op-앰프

- __오디오

- __필터와 발진기

- __전원, 전원 조정, 제어

- __광학과 빛

- __고속 디지털과 RF

- __디지털 신호 처리와 통신

- __로직, 변환, 혼성-신호

- __컴퓨터와 프로그래밍

- __기타

- 부록 O. 오실로스코프

- O.1 아날로그 오실로스코프

- O.1.1 수직

- O.1.2 수평

- O.1.3 트리거 걸기

- O.1.4 초보자를 위한 안내

- O.1.5 탐침

- O.1.6 접지

- O.1.7 다른 아날로그 스코프 기능

- O.2 디지털 오실로스코프

- O.2.1 다른 점

- O.2.2 주의점

- 부록 P. 약자

도서 오류 신고

정오표

정오표

[p.35 2열 마지막 줄 - p.36 1열 2번째 줄]

측정 단위는 볼트이고 전압은 보통 볼트, 킬로볼트, 밀리볼트, 마이크로볼트(접두어 박스 참고).

->

측정 단위는 볼트이고 전압은 보통 볼트, 킬로볼트, 밀리볼트, 마이크로볼트(접두어 박스 참고)로 표시된다.

[p.37 1.2.2 절 제목]

저항과 전류의 관계: 저항

->

전압과 전류의 관계: 저항

[p.37 : 주석 5 위치 3행으로 이동]

전류 ‘앰퍼리지amperage’라고 하지 마라.5

[p.1153 Appendix A.1에서 6행]

cos(x+-y)=cosxcosy +- sinxsiny

->

cos(x+-y)=cosxcosy -+ sinxsiny

[p.1153 Appendix A.1에서 오른쪽 6행]

loge (x/y) = loge x + loge y

->

loge (x/y) = loge x - loge y

[p.1154 : 수식 2행]

(a+ib)(c+id)=(ac-bd)+(i(bc-ad)

->

(a+ib)(c+id)=(ac-bd)+(i(bc+ad)

[p.1154 : 수식 3행]

수식의 마지막 항의 분자는 bc-ad로 변경

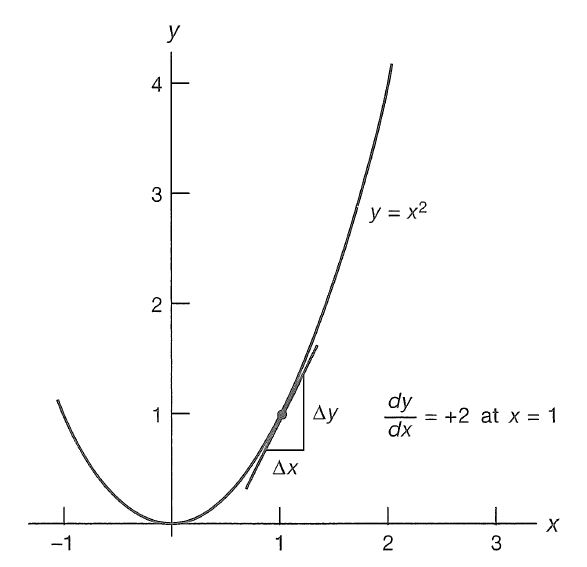

[p.1155 : 그림 A.3 일가함수 f(x) = x^2]